| |

Inhaltsverzeichnis

- 1 ATMEL Microcontroller

- 1.1 Controllerangebot

- 1.2 ATMEL AVR

- 1.2.1 Tiny / Standard / Mega

- 1.2.2 Projektunterstützung

- 1.2.3 Beispielschaltungen

- 2 Der CAN-Bus

- 2.1 Geschichte

- 2.1.1 Normung

- 2.1.2 Spezifikationen

- 2.2 Datenübertragung

- 2.2.1 Nachrichtenaustausch

- 2.2.2 Data-Frame

- 2.3 Fehlertoleranz

- 2.4 Lösungen am Markt

- 2.5 Einfaches SJA1000-Interface

- 2.5.1 Referenzdesign / Elektorlösung

- 2.5.2 Eigenentwicklung

- 3 Quellenangabe

Hinweis: da der Vortrag auf ca. 1h angesetzt ist, ist nur ein grober Überblick realisierbar! Man könnte mit beiden Teilthemen problemlos mehrere Stunden, mit CAN wohl auch Tage füllen ;)

| |

| |

1 ATMEL® Microcontroller

ATMEL® - Wer/was ist das?

- US-amerikanischer Halbleiterhersteller

- Gründung 1984

- Design, Herstellung, Vermarktung von hochintegrierten Schaltkreisen

- tätig in nahezu allen bedeutenden Mikroelektronikbereichen:

- Verbraucherelektronik (z.B. diverse Analog-/Digitalschaltungen, Radio-ICs)

- Kommunikationstechnik (z.B. WLAN, Bluetooth)

- (Mikro-)Computer-, Netzwerktechnik

- Sicherheitstechnik

- Industrie- und Pharmaziebedarf

- Fahrzeug und Luftfahrttechnik

- Anwendungen für militärischen Einsatz

- Handhelds mit hohem Rechenbedarf bei niedrigem Stromverbrauch

- aktuell Migration auf 0.13µ-Technik

- auch durch nichtflüchtigen Speicher (DataFlash) bekannt

- große Auswahl von Microcontrollern für unterschiedlichste Einsatzzwecke

| |

| |

1 ATMEL® Microcontroller

1.1 Controllerangebot

- 8051 Architektur, auch C251 - 8 Bit CISC (AT87/89)

- ISP, mit und ohne ROM, Flash, teilweise High-Speed-Core (x2)

- CAN, TCP/IP

- MP3, Smart Card Reader, USB

- ARM-CPUs - 8/16/32 Bit RISC (AT91)

- Billigsegment ARM7, Highendsegment ARM9 mit bis zu 200 MIPS

- diverse Peripherie (USB, 10/100 Base T, ...)

- Plattform für ASIC/ASSP

- AVR - 8 Bit Risc (siehe 1.2)

- Marc4 - 4 Bit RISC

- optimal für batteriegebundene Systeme, Stromaufnahme unter 1 mA

- max. 4 MHz, 2 Taktzyklen pro Befehl

- Oszillatoren, Watchdog-Timer, serielle Ports, ...

- Spezialcontroller:

- FPSLIC - in FPGA integrierter AVR

- CAN-Controller mit integriertem 80C51 oder AVR

- DSP - Dual-CPU-Prozessor mit integriertem ARM7 und bis zu 10 Befehlen pro Takt bei 100 MHz

- USB-Controller, auch inkl. 80C51 oder AVR

Applikationsspezifische Standardprodukte (ASSP - application specific standard product) - ein Logikschaltkreis, dessen Funktion fest definiert ist, der jedoch von mehreren Kunden genutzt werden kann (z.B. Applikationsprozessor für Handys)

Kundenspezifische Integrierte Schaltung (ASIC - application specific integrated circuit) - ein Logikschaltkreis, dessen Funktion ebenfalls fest definiert ist, der aber speziell für einen Kunden bzw. eine Anwendung entworfen und gebaut wird (In der Praxis werden mit diesem Begriff häufig auch alle festdefinierten Logikbausteine assoziiert - ASIC und ASSP)

The Atmel PSLI (Programmable System Level Integration) University Program provides qualified Universities access to leading-edge SoC silicon and design tools as well as classroom and laboratory materials.

| |

| |

1 ATMEL® Microcontroller

1.2 ATMEL® AVR

- ursprünglich norwegisch/schwedisches Design

- hervoragende Alternative zu Intels 8051, Motorolas 6805/68HC11, PICs usw.

- Entwicklung in Zusammenarbeit mit Compilerherstellern

- 2 getrennte Busse => Harward-Architektur (16 Bit Befehlsbus, 8 Bit Datenbus)

- Program Counter 9 bzw. 16 Bit breit

- nur AT90S1200: 3-Level-Hardwarestack ohne SRAM

- Flashspeicher (1000 Schreibzyklen) - auch für Konstanten oder Variablen nutzbar

- SRAM: 32 Byte Register, 64 I/O-Register, ab $60 interner SRAM, externes SRAM bis insg. 64k mgl.

- EEPROM, Datenspeicher mit getrenntem Adressraum, Zugriff über Spezialregister

- 8-/16-Bit Timer und Counter, Echtzeituhr teilweise mgl.

- Watchdogtimer mit eigenem Oszillator zuschaltbar, per Prescaler auf ca. 2,048s streckbar

- Programmierung über ISP, serielle oder parallele Anschlüsse

| |

| |

1 ATMEL® Microcontroller

1.2 ATMEL® AVR

1.2.1 ATtiny, Standard-AVR, ATMega

Kenndaten

- AVR Classic (AT90), ATtiny, ATMega

- interne Oszillatoren, Timer, UARTs, SPI, Pull-Up-Wid., ADC, Analog-Komparatoren, LCD-Controller ...

- 128 Byte - 128kByte Flash, 64 Byte - 4kB EEPROM, 32 Byte bis 4KByte SRAM (außer AT90S1200)

- 32 Allzweckregister, Befehlssatz mit 120 Befehlen

- hochsprachenoptimiert, echter RISC ohne Taktteilung bei bis zu 20 MHZ

- sehr geringe Stromaufnahme, zusätzlich Lowvoltage-Versionen (2-8 MHz)

Warum gerade dieser Prozessor?

- extrem hohe Beliebtheit auch im Hobbybereich => viele Bsp. verfügbar

- google findet:

- Ergebnisse 1 - 10 von ungefähr 304.000 für atmel avr

- Ergebnisse 1 - 10 von ungefähr 48.400 Seiten auf Deutsch für atmel avr

- sehr preisgünstig, leicht zu beziehen

- große Auswahl für unterschiedlichste Anforderungen

- ... und Punkt 1.2.2 ...

| |

| |

1 ATMEL® Microcontroller

1.2 ATMEL® AVR

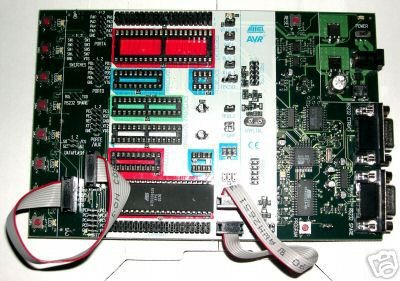

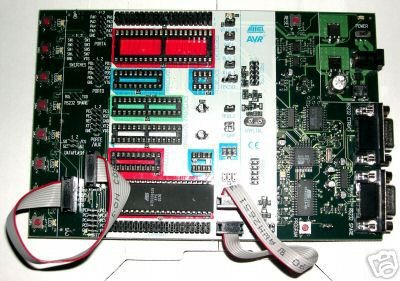

1.2.2 Projektunterstützung

Entwicklungssoftware

Evaluationsboards

- unzählige "Selbstbau-Testboards" verfügbar aus Büchern, Zeitschriften oder Internet

- Boards nach STK200/300-Standard für ca. 50 Euro erhältlich

- aktueller Standard: STK500, Preis ca. 100 Euro

- Erweiterungen STK501/502, Preis je ca. 90 Euro

- Spezialboards für viele Anwendungen verfügbar (z.B. für CAN)

| |

| |

1 ATMEL® Microcontroller

1.2 ATMEL® AVR

1.2.3 Beispielschaltungen

Fachliteraturbeispiele:

- AVR-Microcontroller-Praxis (S. Volpe, F.Volpe)

- Touch-Memories ("Knopfzellenspeicher"), EEPROM über I2C-Bus, LCD-Anzeige, Telefon-/Magnetkartenleser

- AVR-Risc Mikrocontroller (Trampert)

- LCD-Ansteuerung, AD/DA-Wandler, Frequenzgenerator, Temperatursensor

Umschalter Tastatur/IR-Fernbedienung mit PC-Ausschaltautomatik

- Entwicklung gemeinsam mit Markus Tietke (D4TI)

- 2x ATMega8 bei 3.6864 MHz

- 1. Prozessor für IR-Empfang, schickt Daten per serieller Schnittstelle an 2. Proz.

- 2. Prozessor für Scancodeauswertung, Countdown/Shutdown, 7-Segment-Anzeige, Ausgabe

- Software in BASCOM, Verwendung von zusätzl. kommerz. Bibliotheken

- Source ATMega8 #1 ATMega8 #2

Testprogramm für LEDs und Taster

- Zielprozessor ATMega8515, BASCOM, Source #1 #2

| |

| |

| |

| |

2 Der CAN-Bus

Was CAN der Bus?

Was ist ein Bus?

- Feldbussysteme - spezialisierte busbasierte Netzwerke in einem kleinen (Um-)feld

- CAN

- ControlNet

- PROFIBUS

- INTERBUS

- Vorteile: weniger Kabel/Gewicht, kurze Signalwege, Schutz gegen Störsignale, flexible Erweiterbarkeit, Standardisierung

- Nachteile: geringfügig höhere Reaktionszeit, Komponenten teurer

Buszugriffsverfahren

- Unterscheidung in deterministisch - zentral/dezentral gesteuert und zufällig - (nicht) kollisionsfrei

- Master-Slave-Verfahren

- Delegated Token

- Token Passing

- TDMA (Time Division Multiple Access)

- CSMA/AD (Carrier Sense Multiple Access Collision Avoidance)

- CSMA/CD (Carrier Sense Multiple Access Collision Detect)

| |

| |

2 Der CAN-Bus

2.1 Geschichte und Allgemeines

- seit 1983 von BOSCH vorrangig für KFZ-Bereich entwickelt

- Ziel: Reduzierung der oft bis über 2km langen Kabel (100kg)

- notwendig für zentrale Steuerung von Fensterhebern, Spiegel- und Sitzeinstellung, Motormanagement, ABS, ESP, Klima, ...

- heute: KFZ der Oberklasse mit ca. 100 Mikrocontrollern

- Notwendigkeit für:

- hohe Fehlertoleranz

- Optmierung auf kleine Datenmengen

- mgl. einfache und billige ICs

- einfacher Busaufbau

- verschiedene andere Bussysteme zugunsten von CAN eingestellt

- seit 1992 Einsatz bei Mercedes, heute von fast allen Automobilkonzernen genutzt

- Interesse auch von Industrie => messen, steuern, regeln (Bsp.: Aufzüge)

- Ergebnis: simple Handhabung, große Verbreitung und (genormte) Produktvielfalt, günstige Preise

| |

| |

2 Der CAN-Bus

2.1 Geschichte und Allgemeines

2.1.1 Normung

- ISO/OSI-Referenzmodell

- Physical Layer (1) - Low-Speed-CAN ISO 11519-2 (5-125 kBit/s) und High-Speed-CAN ISO 11898 (max. 1 MBit/s)

- Data Link Layer (2) - Logical Link Control, Medium Access Control nach ISO 11898 => CAN 2.0A, CAN 2.0B

- Application Layer (7) - CAL (CAN Application Layer for industrial Application), Spezifikationen für DeviceNet und SDS (Smart Distributed System)

- Layer 8 - CANopen, DeviceNet, SDS

- Normung und Weiterentwicklung von CiA (CAN in Automation) http://can-cia.de

| |

| |

2 Der CAN-Bus

2.1 Geschichte und Allgemeines

2.1.2 Spezifikationen

- Unterscheidung:

- CAN (laut 2.0A/2.0B max. 32 Teilnehmer)

- CANopen (vorrangig Industrieautomatisierung, Datenfeld wird für Objektadressierung mitgenutzt, enthält Synchronisationsprotokoll)

- DeviceNet (max. 64 Teilnehmer, meist mehrere Identifier pro Teilnehmer)

- Busrealisierung mit TP-Kabeln, Anschlüsse meist 9-pol. SUB-D, Abschlußwid. ca. 120 Ohm

- CSMA/CA auf 2 Leitungen (CAN_HIGH, CAN_LOW), meist auf 3. Leitung (Schirm) CAN_GND

- Spannungsversorgung über Bus optional mgl.

- max. Datenübertragungsrate 1 Mbit/s bis 40m, 125 kbit/s bis 500m

- Differenzspannungen nach ISO11898:

- rezessive Bits (Potential CAN_GND +0...0,5V)

- dominante Bits (Potential CAN_GND +0,9...2,0V)

- verschiedene fertige Tranceiver verfügbar

- weiterhin genormt: Busanzapfungen, Interfaceanschlußstecker

- auch andere als hier erwähnte Realisierungen am Markt (z.B. einadrige Bussyteme, andere Differenzspannungen, (dynamisches) Zeitschlitzverfahren als Ergänzung zum CSMA/CA)

| |

| |

2 Der CAN-Bus

2.2 Datenübertragung

2.2.1 Nachrichtenaustausch

- allgemeine Unterscheidung in:

- teilnehmerorientiert (z.B. TCP/IP)

- objektorientiert (z.B. CAN)

- Priorisierung (über Identifier)

- 0 = dominant, 1 = rezessive

- Verwendung von CAN-Frames:

- Data-Frame

- Remote-Frame

- Error-Frame

- Overload-Frame

- 0-8 Byte Daten im Data-Frame

- 11-Bit-Identifier nach CAN 2.0A (max. 2,032 Objekte, Framelänge max. 117 Bit)

- 29-Bit-Identifier nach CAN 2.0B (max. 536,870,896 Objekte, Framelänge max. 136 Bit)

| |

| |

2 Der CAN-Bus

2.2 Datenübertragung

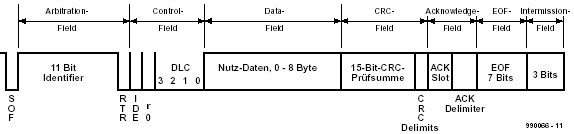

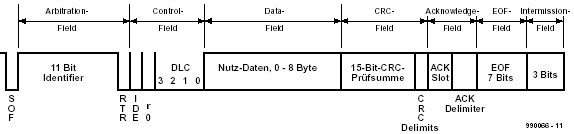

2.2.2 Data-Frame

Quelle: Elektor 10/1999 Quelle: Elektor 10/1999

- Start of Frame (dominantes Bit)

- Arbitration Field (11 Bit Identifier, Remote Transmission Request Bit)

- Control Field (Identifier Extension-Bit (rezessiv => 29-Bit-Identifier), dominantes Reserve-Bit 0)

- Data Length Code

- Data-Field

- CRC-Field (15 Bit Checksumme, 1 dominantes Bit)

- Acknowledge-Field (ACK-Slot wird rezessiv gesendet, Empfänger überschreibt bei Erfolg dominant)

- EOF-Field (7 rezessive Bits)

- Intermission-Field (3 Bit Pause auf Bus für Datenverarbeitung durch Clients)

| |

| |

2 Der CAN-Bus

2.3 Fehlertoleranz

- Hamming-Distanz HD=6 (Feldbus allg. mind. 4, Wikipedia, Hamming-Abstand)

- 5 Fehlererkennungsstrategien bei CAN:

- Bit-Fehler-Erkennung (Selbsttest der gesendeten Daten)

- Stuffbit-Fehler-Erkennung (max. 5 gleiche Bits in Folge, dann Komplementärbit, Ausnahme EOF-Field)

- CRC-Fehler-Erkennung (Integritätscheck Daten-CRC-Summe)

- Acknowledgement-Fehler-Erkennung (mind. 1 Empfänger muß ACK-Slot-Bit dominant überschreiben)

- Format-Fehler-Erkennung (Erkennung von dominanten Bits an rezessiven Stellen)

- bei erkanntem Fehler:

- Nachricht wird verworfen

- Senden eines Error-Frames mit 6 dominanten und 8 rezessiven Bits

- Sender erkennt Fehler ebenfalls und wiederholt später die Nachricht

- CAN enthält Konzepte für stationsinterne Fehler

| |

| |

2 Der CAN-Bus

2.4 Lösungen am Markt

- Unterscheidung BasicCAN, FullCAN (Filterung, Speichertiefe)

- fast alle namhaften Hersteller von ICs bieten CAN-Lösungen an

- Stand-alone Controller:

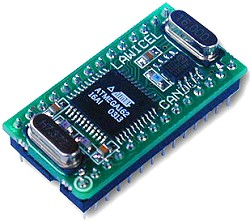

- Philips SJA1000 (Nachfolger vom 82C200), sehr stark verbreitet, oft auch integriert, Modul CANDIP

- Intel 82527

- Microchip MCP2510

- OKI MSM9225

- Infineon 82C900

- Bosch C_CAN

- mit integr. Microcontroller:

- Atmel T89C51CC01

- Dallas DS80C390

- Infineon C515C/C505C/C167CS

- Philips P8xC592/P8xC591/XA C3

- auch erhältlich: Controller mit CAN-Multiplexer, I/O mit CAN, ASICs mit CAN

- CAN-Tranceiverbausteine

- Infineon TLE 6250/TLE 6254 G/TLE 6255 G/

- Philips 80C250/80C251/80C252/TJA 1050/TJA 1054

- Motorola MC 33388

| |

| |

2 Der CAN-Bus

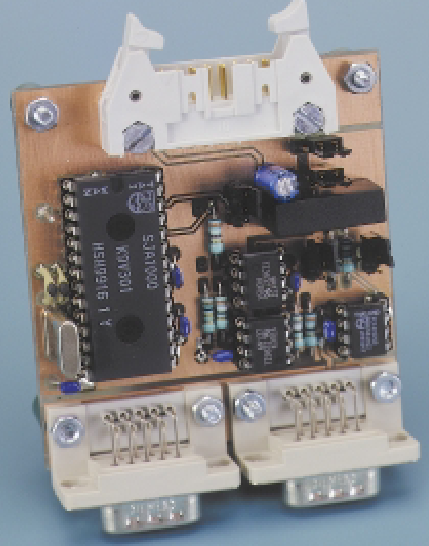

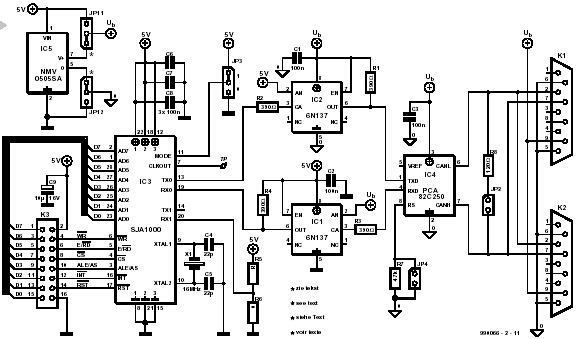

2.5 Einfaches SJA1000-Interface

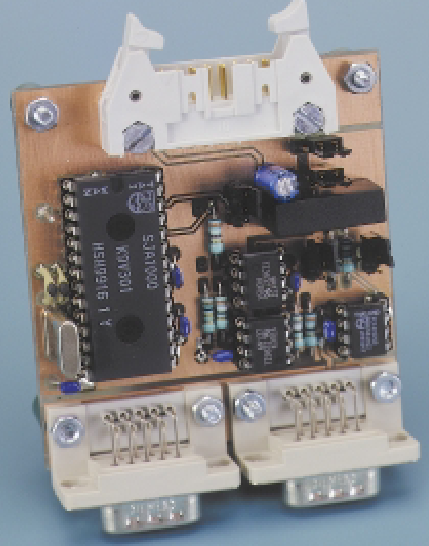

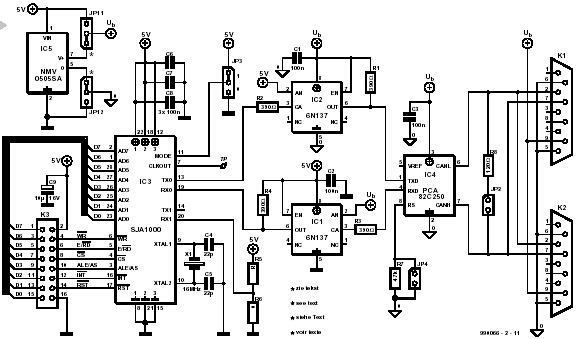

2.5.1 Referenzdesign / Elektorlösung

Quelle: Elektor 11/1999 Quelle: Elektor 11/1999

- wichtige Datasheets/Appnotes:

| |

| |

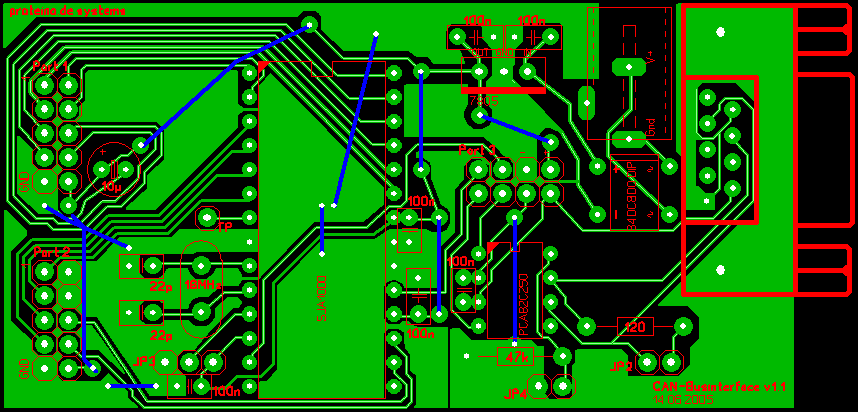

2 Der CAN-Bus

2.5 Einfaches SJA1000-Interface

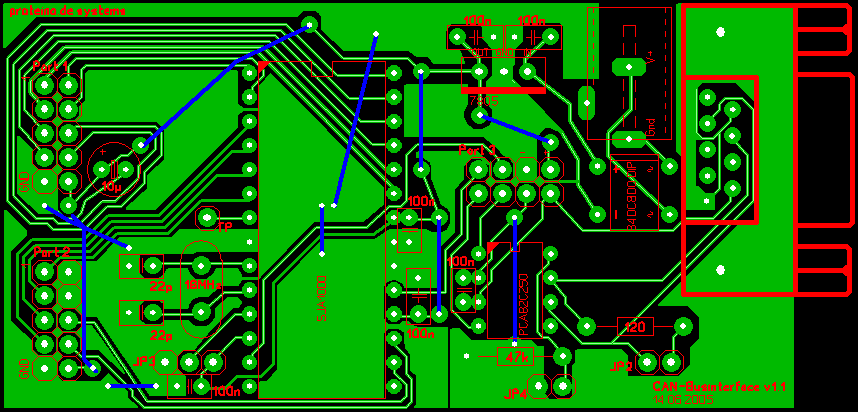

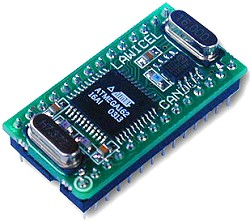

2.5.2 Eigenentwicklung

- angelehnt an Elektorlösung, aber 1-seitige Platine

- Microcontroller über Port 1/2 und Busabkopplung über Port 3 steckbar

- integrierte Spannungsversorgung mit Gleichrichter und 5V-Spannungsregler

| |

| |

3 Quellenverzeichnis

- diverse Ausgaben der Elektor, vorrangig von 1999/2000/2004

- Applicationnotes der vorgestellten ICs

- http://reichelt.de und andere Internetseiten - Pinbelegungen, Rastermaße, AppNotes

- http://elmicro.com/de/candip.html

- Programmieren der AVR RISC Mikrocontroller mit BASCOM-AVR (Claus Kühnel, Skript Verlag Kühnel, 2.Auflage)

- Controller Area Network (Konrad Etschberger, Hanser-Verlag, 3. Auflage)

- CAN Controller Area Network (Wolfhard Lawrenz, Hüthig-Verlag, 4. Auflage)

- weitere Quellen wurden im Text genannt, meist inkl. Link

| |

Quelle: Elektor 10/1999

Quelle: Elektor 10/1999

Quelle: Elektor 11/1999

Quelle: Elektor 11/1999